IT之家 12 月 14 日消息,据 InterestingEngineering 报道,美国工程师研发出一种具有独特架构的新型多层计算机芯片,有望开启人工智能硬件新纪元。

研究团队指出,在硬件测试和仿真中,这款新型三维(3D)芯片的性能比传统二维(2D)芯片高出近一个数量级。

据IT之家了解,与当前主流的平面化 2D 芯片不同,该新型原型芯片的关键超薄组件如同摩天大楼的楼层般垂直堆叠,其内部的垂直布线则如同大量高速电梯,可实现快速、大规模的数据传输。该芯片凭借创纪录的垂直互连密度以及精心交织的存储单元与计算单元,有效规避了长期制约平面芯片性能提升的瓶颈问题。

斯坦福大学电气工程系 William E. Ayer 讲席教授、计算机科学教授、同时也是描述该芯片成果论文的主要负责人 Subhasish Mitra 表示:“这为芯片制造与创新开启了一个新时代。正是此类突破,才能满足未来人工智能系统对硬件性能千倍提升的需求。”

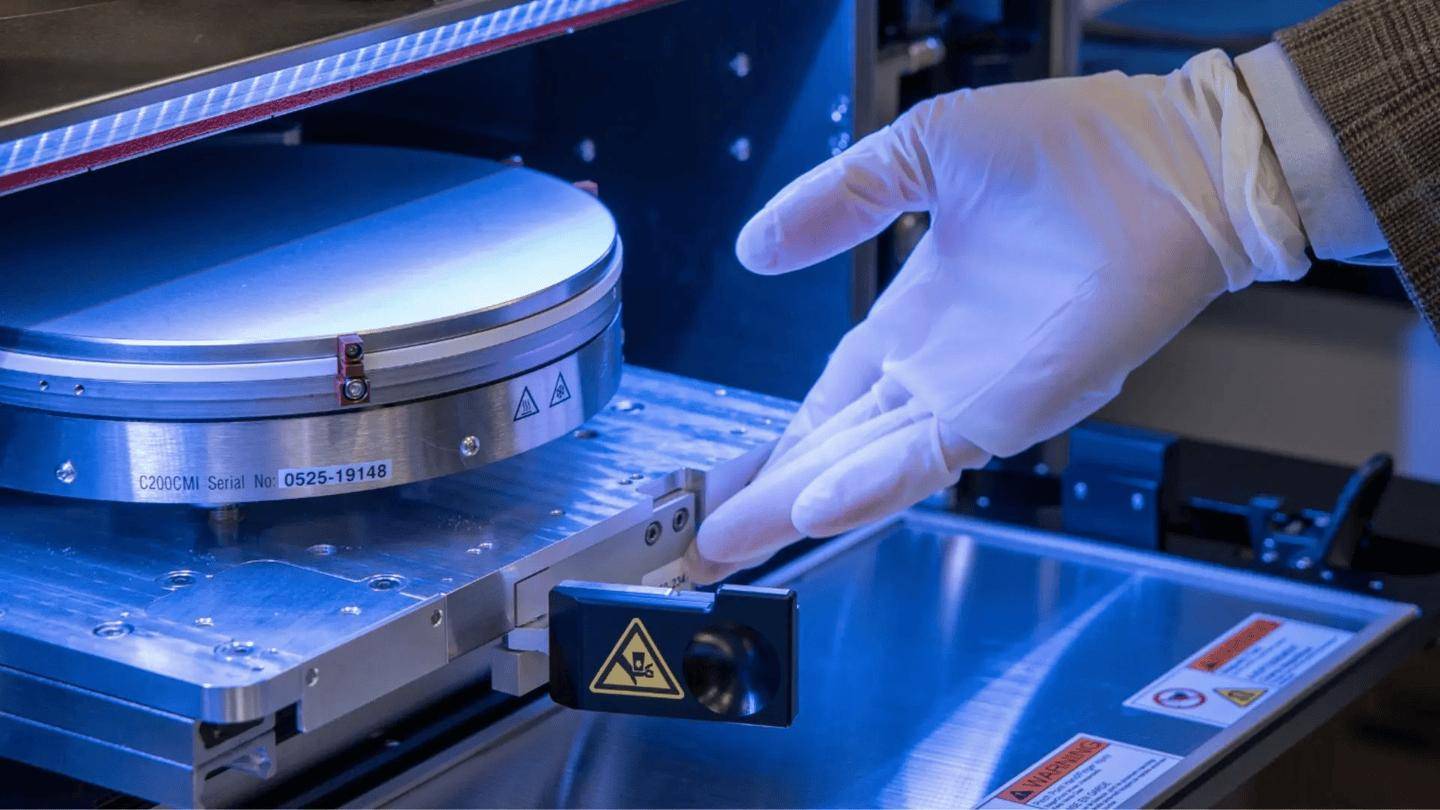

尽管学术界此前已研制过实验性 3D 芯片,但此次是首次在商业晶圆代工厂成功制造出具备明确性能优势的 3D 芯片。

研究团队还指出,在传统 2D 芯片上,所有组件都布置于单一平面,内存分布稀疏且有限,数据只能通过少数几条冗长而拥挤的路径传输。由于计算单元的运行速度远快于数据移动速度,同时芯片无法在附近集成足够内存,系统常常被迫等待数据,这一现象被工程师称为“内存墙”(memory wall),即处理速度超过芯片数据传输能力的临界点。

卡内基梅隆大学电气与计算机工程助理教授、该论文资深作者 Tathagata Srimani 表示:“通过将内存与计算单元垂直集成,我们可以更快地传输更多数据,就像高层建筑中的多部电梯能同时运送大量住户上下楼层一样。”Srimani 最初是在 Mitra 指导下从事博士后研究时启动了这项工作。

斯坦福大学、卡内基梅隆大学、宾夕法尼亚大学和麻省理工学院的工程师们与 SkyWater Technology 公司合作开发了这款 3D 芯片。

初步硬件测试显示,该原型芯片的性能已比同类 2D 芯片高出约 4 倍。对更高堆叠层数的未来版本进行的仿真表明,性能提升更为显著:在真实 AI 工作负载(包括源自 Meta 开源 LLaMA 模型的任务)下,增加更多层级的设计可实现最高达 12 倍的性能提升。

研究团队还声称,该设计为实现能效-延迟乘积(Energy-Delay Product, EDP)提升 100 至 1000 倍开辟了一条切实可行的路径。EDP 是衡量速度与能效平衡的关键指标。通过大幅缩短数据传输距离并增加大量垂直通路,该芯片能够同时实现更高的吞吐量和更低的单位操作能耗,这种组合长期以来被认为是传统平面架构难以企及的目标。

宾夕法尼亚大学电气与系统工程助理教授、该研究共同作者 Robert M. Radway 表示:“‘内存墙’与‘微缩墙’(miniaturization wall)构成了致命组合。我们通过紧密集成内存与逻辑单元,并以极高密度向上构建,正面迎击这一挑战。这就好比计算领域的曼哈顿 —— 我们能在更小的空间内容纳更多‘居民’。”